## <mark>JOURNAL</mark>

Marie Co

#### table of contents

October 1994, Volume 45, Issue 5

#### **Articles**

Customer-Driven Development of a New High-Performance Data Acquisition System, by Von C. Campbell

A Compact and Flexible Signal Conditioning System for Data Acquisition, by John M. da Cunha

High-Throughput Amplifier and Analog-to-Digital Converter, by Ronald J. Riedel

**On-the-Fly Engineering Units Conversion,** by Christopher P.J. Kelly

Built-In Self-Test and Calibration for a Scanning Analog-to-Digital Converter, by Gerald I. Raak and Christopher P.J.

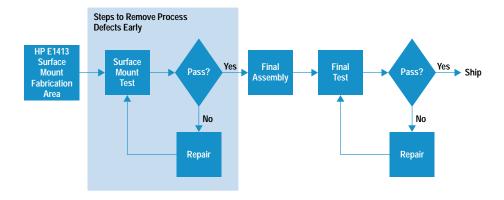

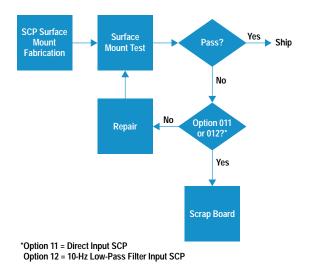

Manufacturing Test Optimization for VXI-Based Scanning Analog-to-Digital Converters, by Bertram S. Kolts and Rodney K. Village

Design Leverage and Partnering in the Design of a Pressure Scanning Analog-to-Digital Converter

by Richard E. Warren and Conrad R. Proft

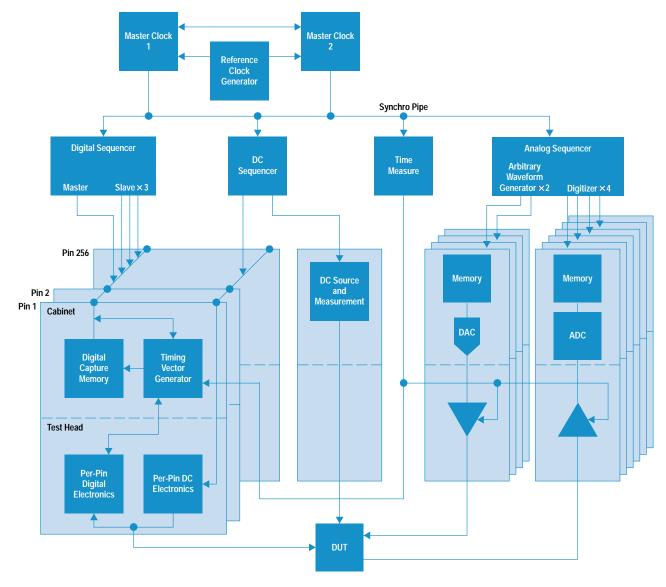

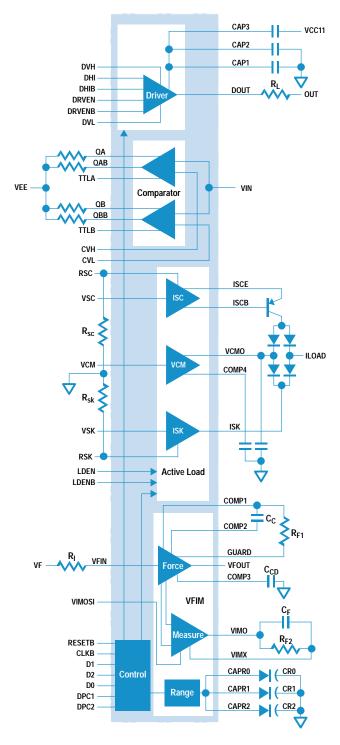

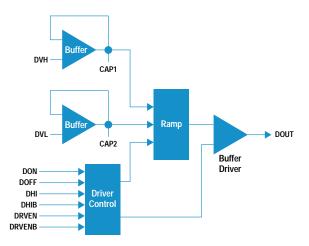

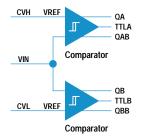

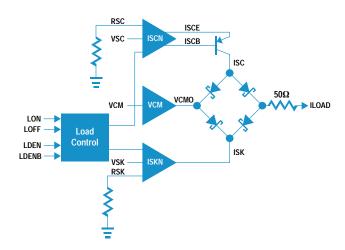

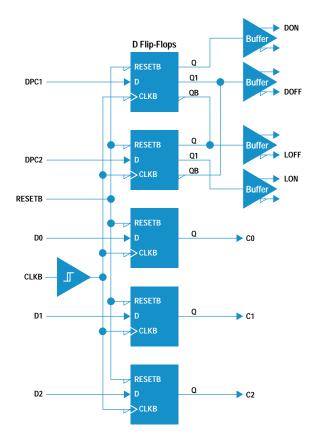

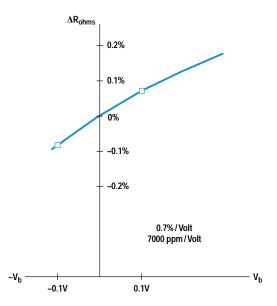

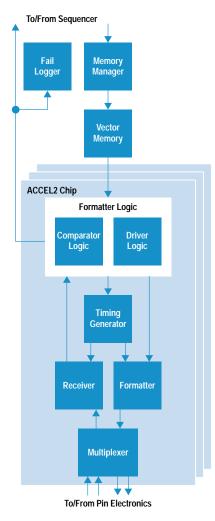

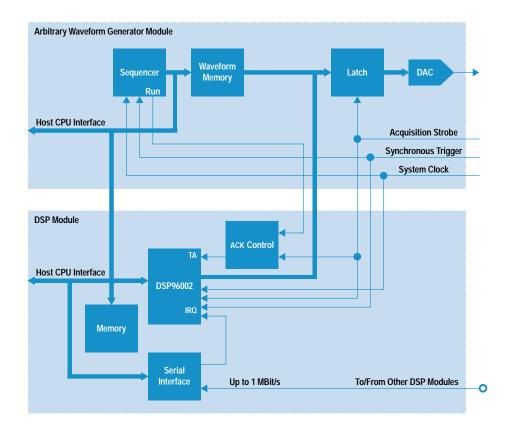

Integrated Pin Electronics for Automatic Test Equipment,

by James W. Grace, David M. DiPietro, Akito Kishida, and Kenji Kinsho

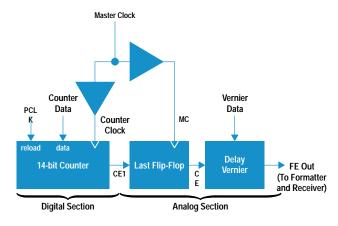

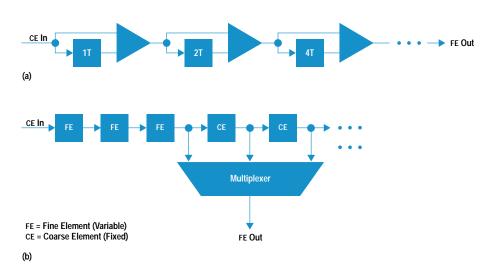

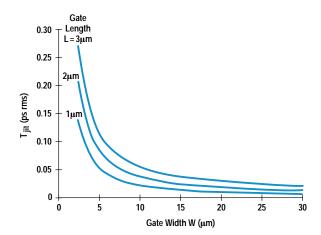

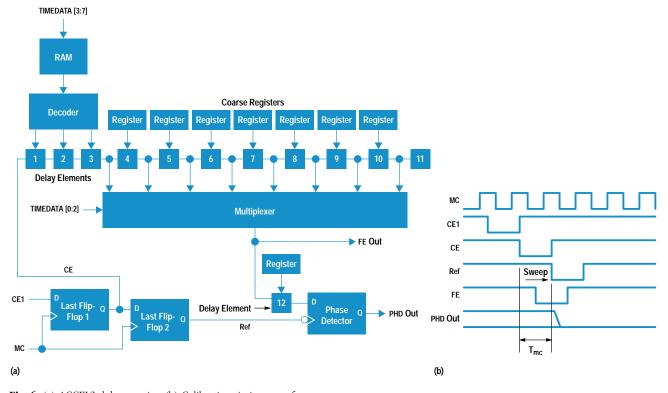

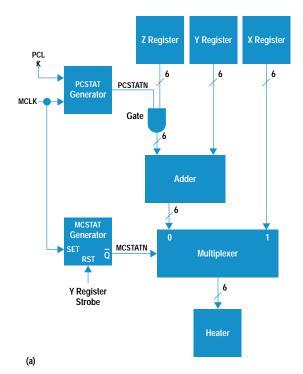

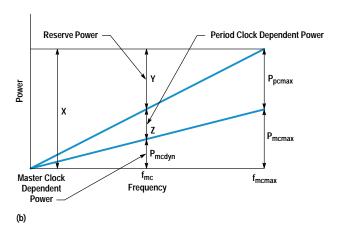

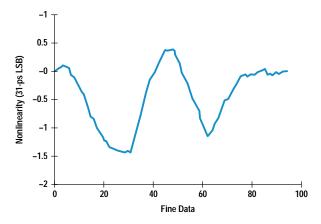

CMOS Programmable Delay Vernier by Masaharu Goto, James O. Barnes, and Ronnie E. Owens

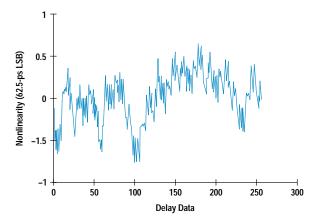

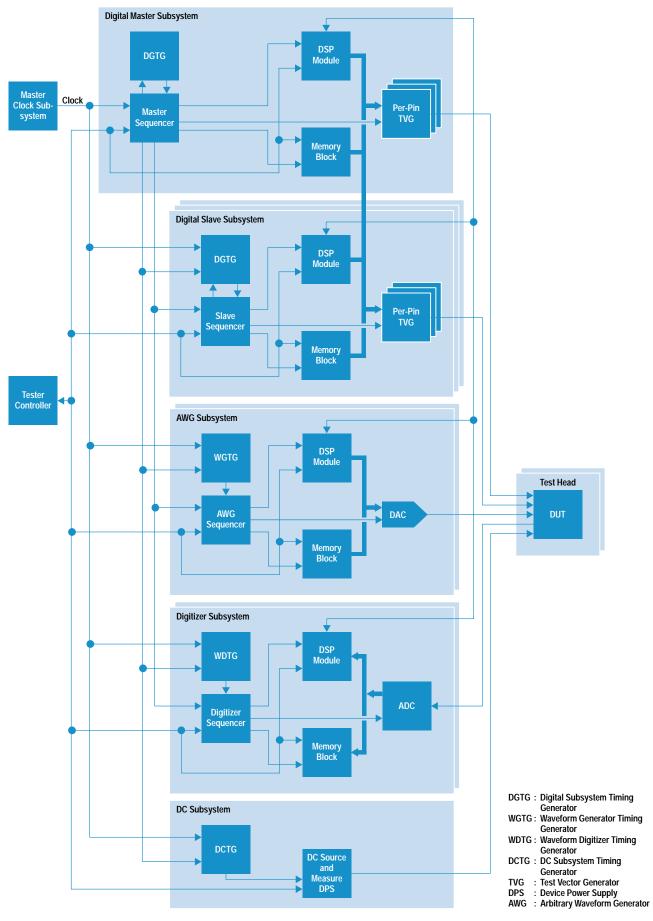

Real-Time Digital Signal Processing in a Mixed-Signal LSI Test System,

by Keita Gunji

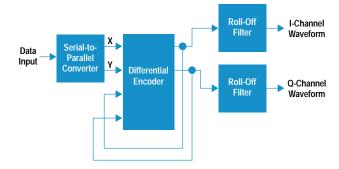

**Vector Error Testing by Automatic Test Equipment,**

by Koji Karube

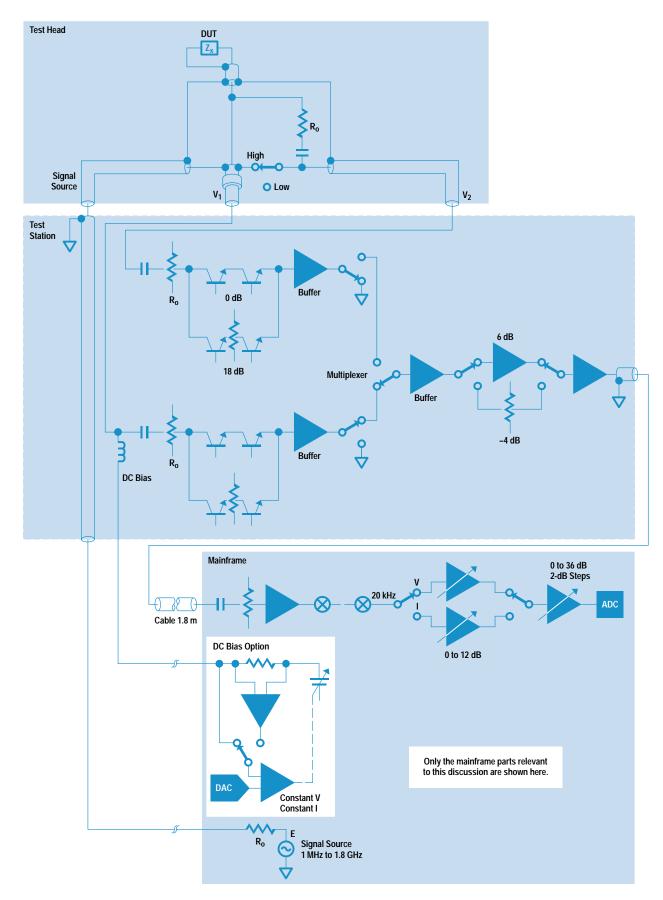

High-Frequency Impedance Analyzer by Takanori Yonekura

**Virtual Remote: The Centralized Expert,** by Hamish Butler

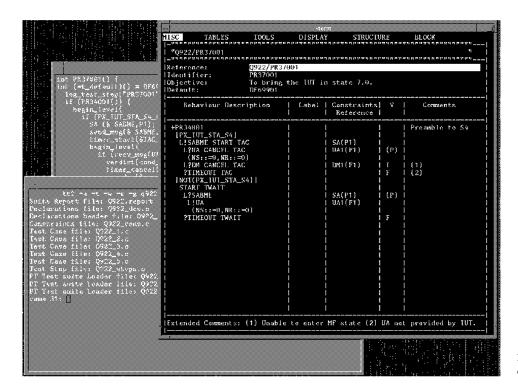

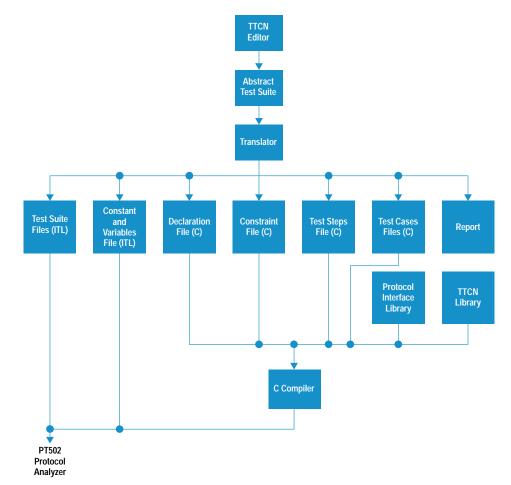

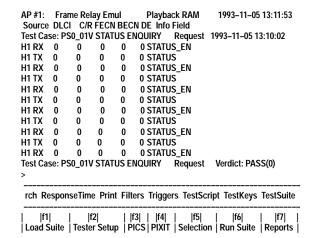

Frame Relay Conformance Testing, by Martin Dubuc

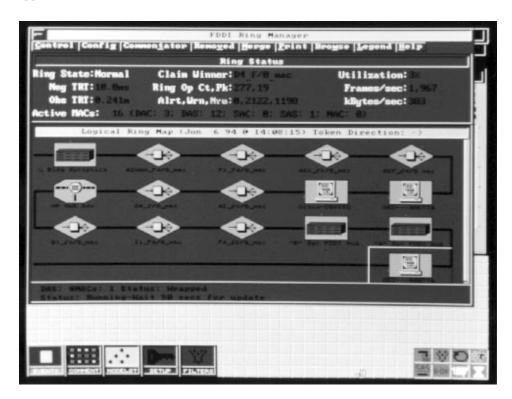

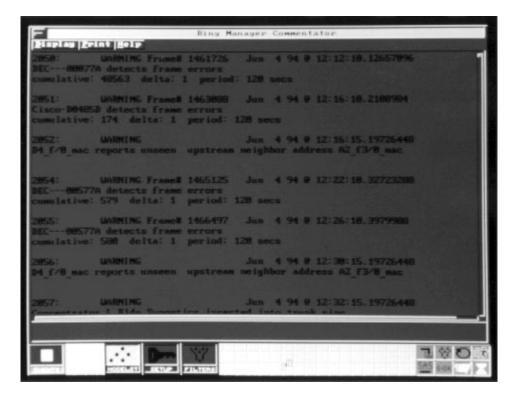

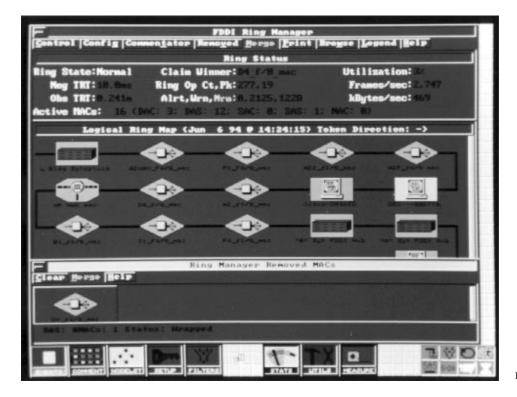

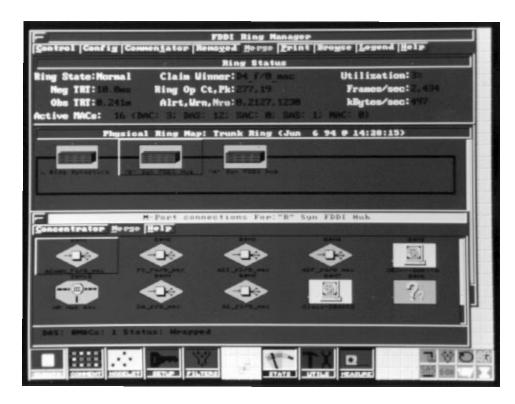

The FDDI Ring Manager for the HP Network Advisor Protocol Analyzer,

by Sunil Bhat, Robert H. Kroboth, and Anne L. Driesbach

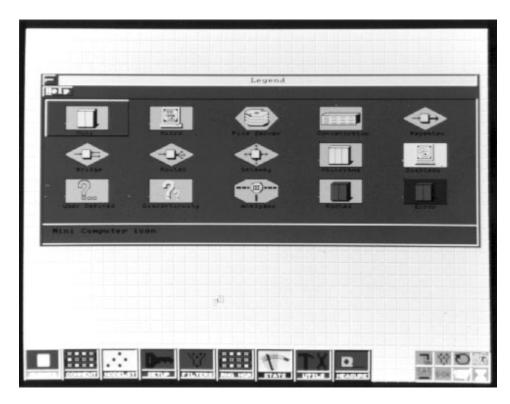

**FDDI Topology Mapping**

by Sunil Bhat

**Automation of Electrical Overstress Characterization for Semiconductor Devices**,

by Carlos H. Diaz

## Customer-Driven Development of a New High-Performance Data Acquisition System

The HP HD2000 data acquisition system provides C-size VXIbus modules that are tailored to provide fast and accurate acquisition of temperature, pressure, strain, volts, and resistance data for turbine and piston engine testing applications.

#### by Von C. Campbell

Products from the past like the HP 2250 measurement and control processor and current products like the HP 3852 measurement/control instruments have given HP a reputation for excellent measurement integrity and throughput. However, within the turbine and piston engine test markets we found certain groups who stated that our measurement products "almost, but not quite" did their job. Obviously there was something in these applications that these products could not do. What was missing? Only customers could tell us.

We undertook an effort to find and talk to turbine and piston engine test customers so that we could understand their applications and the problems they were facing with existing products. These discussions were done in the language of the customer, which required some vocabulary development on our part. After understanding these first applications, we widened our scope to include as many customers as possible. Over 100 customer visits were conducted, including virtually every turbine engine manufacturer and larger piston engine manufacturers worldwide, many being visited more than once.

A very clear picture of these applications emerged. In turbine testing for example, we discovered three use models with similar but distinct measurement needs. The first model was found in engine design and development. In this model large amounts of data (up to thousands of test points per engine) are collected for analysis of the thermodynamic performance of the engine and for verification of the simulation models used in development. The second use model was found in production test of a finished engine immediately after manufacture. Here a smaller test system is used to verify proper engine operation. Finally, the last use model was found in the overhaul and repair of an engine. In this model an even smaller set of data is collected to determine if the engine is performing well enough to be returned to service.

Some common threads ran through all the applications. Accuracy was one of these common features. Temperature measurements to better than 0.25 °C and pressure measurements to 0.05% are required to verify the efficiency of an engine. Engine efficiency is especially important to manufacturers who guarantee fuel consumption rates to their airline

customers. Another important factor is the requirement that the test system be capable of being scaled to accommodate from about 100 to over 2000 measurement points for different sized test systems. Continuous high-speed acquisition, in which data is recorded for long periods without interruption, is also an important factor. Measurement rates of up to 1000 Hz per channel on different sensor types allow a better understanding of the static and transient behavior of the engine, but the aggregate throughput of such large, fast systems is a significant challenge. Older measurement systems used many independent instruments to record the volume and variety of data taken during a test. After the test, all the various data records had to be combined to form a single integrated picture of test results. To overcome this problem of data integration it is imperative that all data be measured and recorded deterministically.

One common need that goes beyond the acquisition system is the industry-wide pressure on test departments to be more productive. The desire to reduce test times and the resources needed to install, develop, and operate a test system is universal. In some areas, there was a strong desire to have a third party develop and install the test system so that the organization could concentrate on testing. This information led to our getting in touch with the leading systems integrators to understand how we could help them solve their customers' problems.

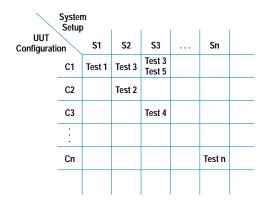

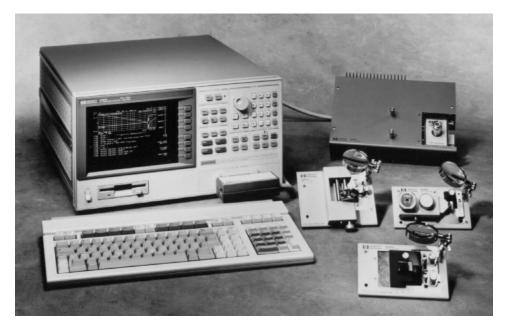

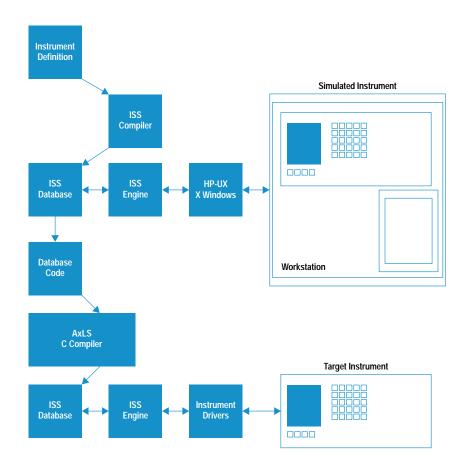

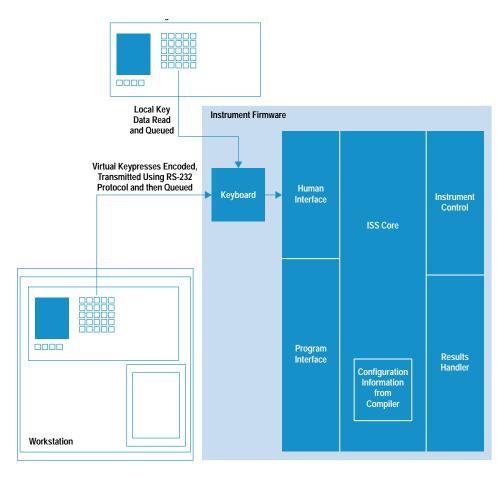

After developing a clear picture of user needs and reviewing past implementations, we came to the conclusion that although individual measurement requirements were being met with existing products, system requirements like those mentioned above were not being met. From this conclusion, the HP HD2000 VXIbus-based data acquisition system was born (see Fig. 1).

VXIbus technology<sup>1</sup> has the right capabilities to meet the system issues we encountered during our customer analysis. The VXIbus architecture allows us to integrate mixed measurements from multiple sources onto one computer bus, allowing high speed and determinism in data sampling. Since VXIbus is an open standard we can include non-HP products that offer specific functions like IRIG B time stamping, MIL STD 1553, and ARINC 429 communications instruments into our system. These products help meet overall systems

**Fig. 1.** The HP HD2000 data acquisition system showing the HP E1413 and HP E1414 modules.

requirements without requiring large additional development time and cost.

#### The Measurement Modules

The bulk of the HP HD2000 system measurements come in the form of analog input, with measurements of temperature and pressure making up about 90% of the volume of data. To meet these needs the HP E1413 64-channel scanning analog-to-digital converter and the HP 1414 pressure scanning analog-to-digital converter were developed. These converters are designed to maximize measurement accuracy, throughput, determinism, flexibility, and density while minimizing computer resource use, program development time, and cost. These modules are the first two modules of the HP HD2000 data acquisition system.

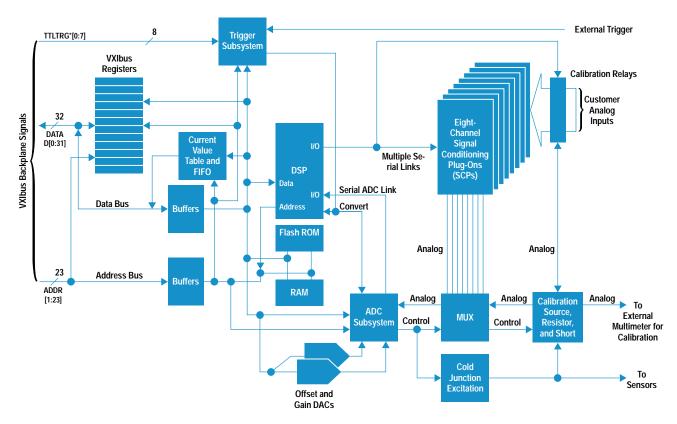

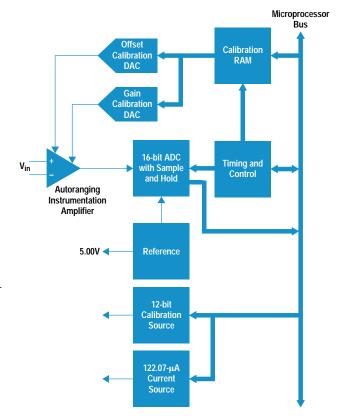

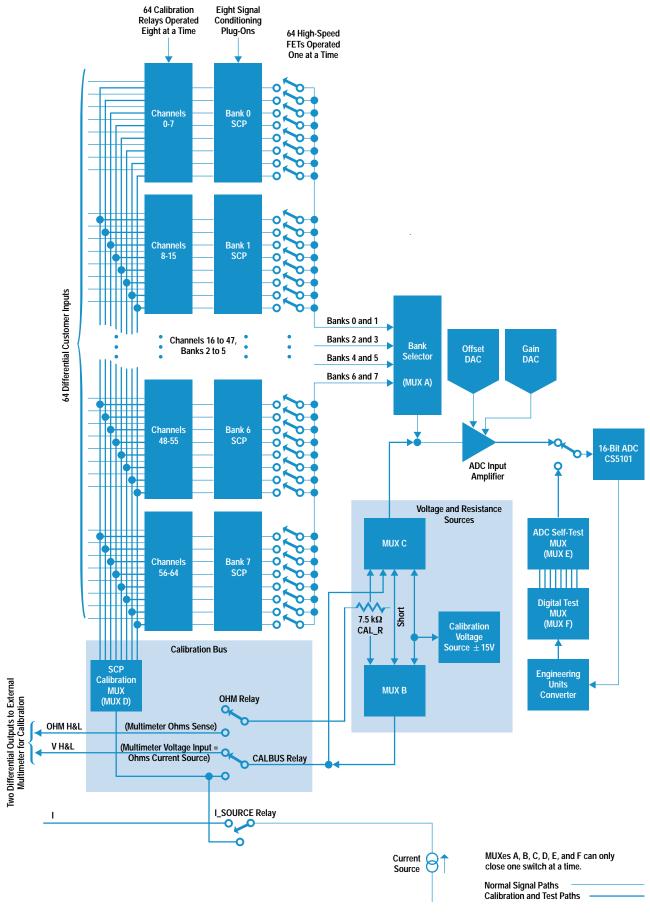

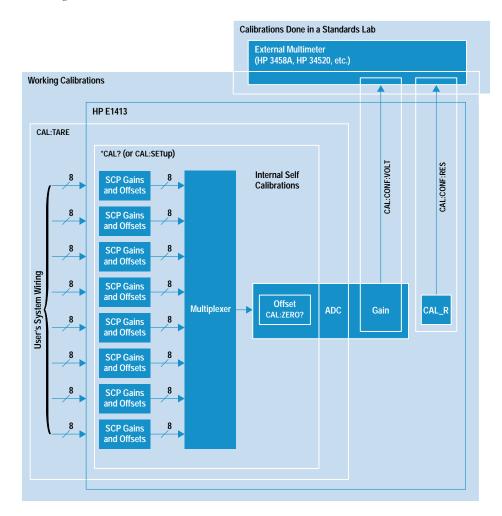

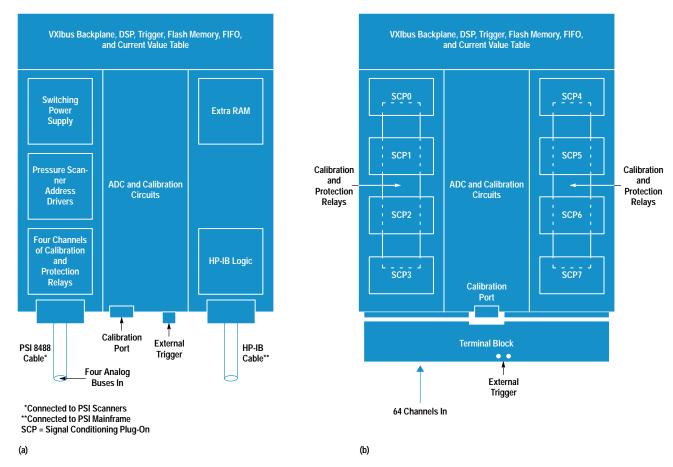

The single-slot HP E1413 combines a highly accurate 100-kHz, 16-bit, autoranging analog-to-digital converter with 64 channels of a high-speed multiplexer and eight banks of front-end signal conditioning plug-ons (such as amplifiers and low-pass filters) and has an internal calibration source for end-to-end calibration. Gain and offset errors for every channel, including signal conditioning, can be removed through the automatic calibration process, maximizing measurement accuracy. An onboard digital signal processor (DSP) controls the card's basic operation, including sequencing of multiple channel scan lists, real-time limit checking, conversion of data to engineering units, and conversion into

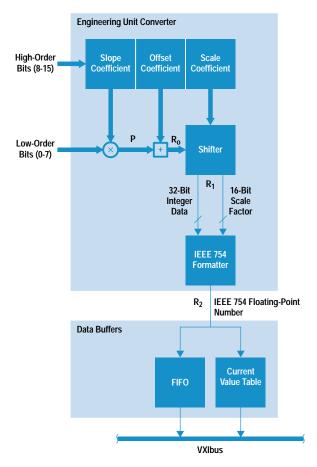

a computer-ready, 32-bit floating-point number. These numbers are output into a 65,000-reading FIFO buffer and a current value table, which allows instant access to the most recent reading on any channel. These features minimize the amount of interaction the card needs to have with the host computer and the amount of work it has to do to make the data interpretable. This tightly coupled architecture maximizes throughput while minimizing the need for external computer resources. Fig. 2 shows a block diagram of the HP E1413.

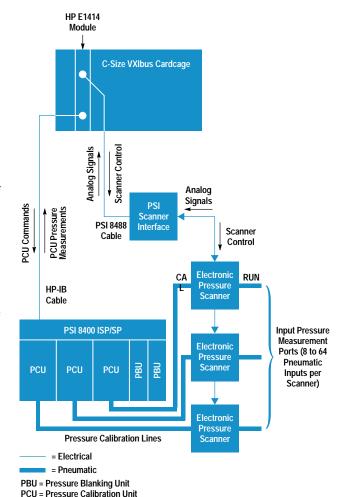

In pressure measurement systems, which typically have a large number of test points, we found that electronic pressure scanning technology is the measurement technology of choice. The recognized leader in this technology is Pressure Systems Inc. (PSI) in Hampton, Virginia. As a continuation of our focus on user needs, we developed a partnership with PSI to develop a pressure scanning analog-to-digital converter. This product, the HP E1414, has all the features of the HP E1413 but is designed to interconnect and operate with PSI's electronic pressure sensors and pressure calibrators. The HP E1414 brings the same level of measurement performance and throughput to pressure measurements as the HP E1413 does for the other analog measurements. It also integrates the deterministic measurements of both temperature and pressure into one common system on the VXIbus backplane.

Fig. 2. A block diagram of the HP E1413 64-channel scanning analog-to-digital converter.

The HP E1413 is described in detail in the articles on pages 9, 16, 21, 25, and 30. The HP E1414 is covered in the article on page 35.

To help minimize customers' development time for the acquisition software, all the products in the HP HD2000 family have drivers that maximize their commonality and performance. These drivers allow the instruments to be controlled using the Standard Commands for Programmable Instrumentation (SCPI) language.<sup>2</sup> This open standard language has a programming syntax that is easy to read and understand, and it has a high level of commonality between many different instruments. This minimizes programming time and enhances supportability. To meet our users' needs for high throughput, a C language preprocessor was developed to process the standard SCPI commands into a format that, along with the driver code, can be compiled into high-speed, run-time code. This compiled SCPI (C-SCPI) gives the programmer the ease of programming in a high-level language and the execution speed of assembly code.

#### Conclusion

The HP HD2000 system began with understanding the users' needs from the perspective of their whole system. This understanding led us to choose the VXIbus architecture, which

provides the high throughput, tight coupling, and mixed-measurement capabilities our customers need. Understanding customer needs focused our development efforts on products like the HP E1413 and HP E1414 and guided our software implementation to maximize performance without increasing development time. Finally, a clear idea of customer needs enabled us to avoid making enhancements to the products that were considered irrelevant to our customers. These enhancements frequently add cost and time to development and complexity and confusion to the end user. We let the customer tell us what was needed.

#### Acknowledgments

I'd like to thank Joe Marriott for all his support during development, Don Miller for his market insight, all the members of the HP E1413 and HP 1414 teams including the C-SCPI developers, and all the people in the Loveland manufacturing center who produce and ship these products every day.

#### References

1. *Hewlett-Packard Journal*, Vol. 43, no. 2, April 1992, pp. 6-80. 2. S.J. Narciso and G.A. Hill, "The VXIbus From an Instrument Designer's Perspective," *Hewlett-Packard Journal*, Vol. 43, no. 2, April 1992, pp. 15-17.

# A Compact and Flexible Signal Conditioning System for Data Acquisition

Because turbine test setups can have up to 1000 test points, special demands are placed on a data acquisition system that must fit a large number of measurement channels into a C-size VXIbus module.

#### by John M. da Cunha

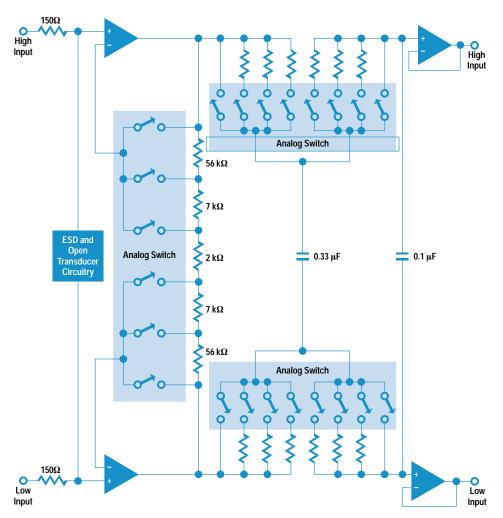

The HP Model HD2000 data acquisition system is targeted for customers in the turbine test market. This market requires a variety of signal conditioning capabilities to make accurate measurements during turbine tests. Special needs include low cost per measurement point, high density, flexibility, and high performance. To take advantage of the HP HD2000 system's high common-mode rejection analog-to-digital converter (ADC), analog signal conditioning has to be fully differential. The variety of functions needed and constraints on cost, density, and the need for high performance presented quite a design challenge.

#### **Customer Needs in Turbine Test**

Turbine test customers use data acquisition systems to characterize, refine, and verify designs of new jet engines and to ensure that engines are performing to specification after overhaul or repair. A typical turbine test system consists of from 100 to 1000 measurement points taking data about engine temperatures, fuel consumption, thrust, pressures, and other items. Data gathered is displayed on control consoles where technicians running the tests can monitor the progress of the test. Data is also sent to disk for storage and later analysis. Because there are so many points in a typical test system, the cost of installing and maintaining each point is high. Thus, low cost per point is very desirable.

Because of the high measurement point count, customers desire that as many channels as possible be put in a single C-size VXIbus module. Therefore, we had to create a design that fits 64 channels of signal conditioning into a single C-size module along with the ADC and the VXIbus backplane interface. The HP HD2000's ADC also has full differential inputs with greater than 110-dB common-mode rejection. The density, cost, and full differential inputs require that signal conditioning circuits be small, inexpensive, and have very high common-mode rejection.

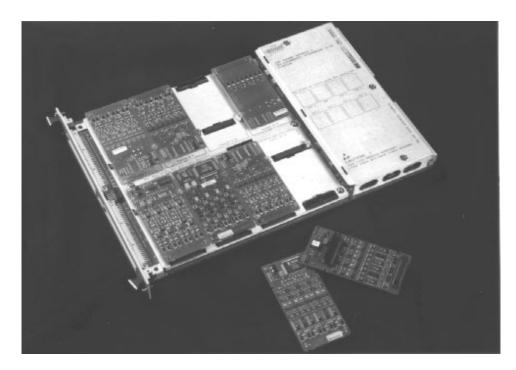

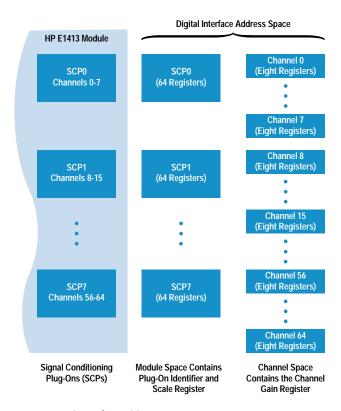

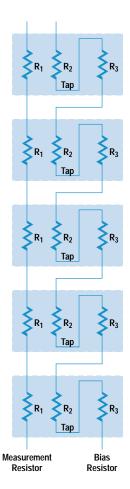

The form factor chosen for these signal conditioning circuits uses a plug-on module for each group of eight channels. Since the HP HD2000 has 64 channels total, this means that each single-width C-size module contains up to eight plug-on signal conditioning circuits with eight channels each (see Fig. 1). These boards are called signal conditioning plug-ons,

or SCPs. Fitting eight SCPs into a single C-size slot meant that we had to create a design in which each SCP could only be 2.00 in by 4.075 in with 1.5 square inches of usable circuit area for each channel. Even using surface mount technology, these constraints proved very challenging for the higher-functionality SCPs.

#### **Required Functions**

The essential signal conditioning functions required by turbine test customers include the ability to:

- · Pass a signal straight to the analog-to-digital converter

- · Provide low-frequency, low-pass filtering

- Provide programmable gain and filtering for lower-noise measurements on thermocouples

- Provide temperature measurements with thermistors and resistive temperature devices

- Measure strain gauges.

The signal conditioning plug-ons (SCPs) in the HP Model HD2000 provide these basic functions.

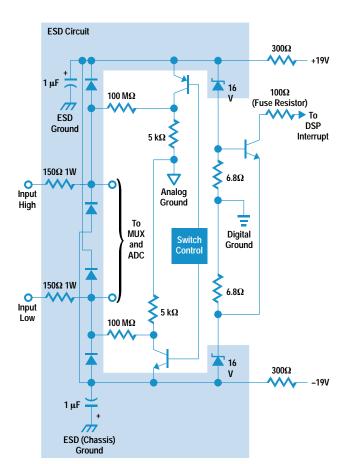

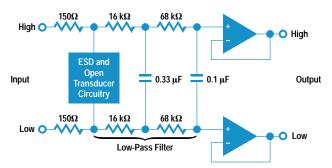

**Straight-Through SCP.** The simplest function required of an SCP is to pass the input directly through to the multiplexer and analog-to-digital converter. We call this the straight-through SCP. The straight-through SCP has additional functionality. Customers want a way to detect an open transducer connection as well as an overvoltage condition. These functions are provided with simple yet effective circuits that yield very good overall results.

Open transducer detection is provided by a very large-value resistor (100  $M\Omega$ ) which can be switched to the positive and negative supplies (see Fig. 2). The resistor provides a very small current that charges the input capacitance to the point where an overvoltage error or nonsensical reading will occur, thereby notifying the operator that there is something amiss with the transducer. Normally, open transducer detection is only switched on during calibration or system verification. The small amount of current will cause a slight degradation of measurement accuracy if used during a data gathering run. While it can be turned on during a data run with no other ill effects, such a practice is not recommended.

**Fig. 1.** An HP E1413 module with the cover off showing the eight (two are removed) signal conditioning plug-ons. Each plug-on has eight channels.

Fig. 2. Open transducer detect, ESD, and overvoltage protection circuit.

Overvoltage protection and ESD (electrostatic discharge) protection are combined into the same circuit for reduced board space and simpler circuitry. Judicious parts placement helped the functionality of the circuits a great deal. The ESD circuit consists of a Zener bias diode with its bias resistor and a large tantalum electrolytic capacitor placed near the ESD ground on the input connector. This provides bias for the diodes that dump static ESD current into the capacitors when the input voltage exceeds ±16.7 volts. ESD current is limited to a manageable value by the physically large, 1-watt, 150-ohm resistors in series with the diodes. Overvoltage protection is provided by monitoring the current through the Zener diode with a transistor. If sufficient current is dumped through the Zener diode, the transistor turns on, sending an interrupt to the digital signal processor (DSP). The DSP will then open protection relays provided on the main board to protect the SCP, the multiplexer, and the ADC. The overvoltage protection feature can also be overridden. Customers override the protection when the cost of stopping the test is more expensive than the measurement system. A fuse resistor is provided to protect the DSP from problems caused by very high overvoltages when the protection feature is overridden. The DSP input is protected by a pair of Schottky diodes that clamp the input. The fuse resistor will open if damage occurs to the input circuits that could put excessive voltage on the DSP input.

Each SCP looks like a memory address segment to the DSP. This memory address segment is called the digital interface address space (see Fig. 3). This address space is divided into two parts on each SCP. One part, called the module space, consists of 64 registers per SCP that are dedicated to addressing functions common to an entire SCP such as the plug-on identifier and scale registers. The other part of the address space, which is called the channel space, consists of 64 registers configured as eight registers per SCP channel.

Fig. 3. Digital interface address space.

This address space is used to address functions unique to each of the eight SCP channels such as channel gain and filter setting.

**Fixed Filter SCP.** A second function required for turbine test is low-frequency, low-pass filtering. Many of the signals from the engine under test represent temperatures measured with thermocouples. Signal voltages are in the millivolt range and subject to high-frequency noise. Low-pass filters with cutoff frequencies of 10 Hz or below are required.

The HP E1413 has only one ADC. Thus, many SCP channels are scanned and multiplexed to the ADC (see Fig. 2 on page 8). With this setup channel-to-channel charge injection through the multiplexer causes errors during fast scanning with passive low-pass filters because the low-pass capacitors hold the charge and cannot dissipate the error charge except through the source and low-pass resistors. For example, if channel 10 on some SCP is holding 6 volts and channel 11 on the same SCP has –15 volts, there is a 21-volt swing when scanning from channel 10 to channel 11, which could cause an error during a fast scan. These errors make it necessary to reduce the scanning speed to achieve the required accuracy. The solution is to buffer the low-pass filter components with an amplifier to absorb the charge injection (see Fig. 4).

As previously stated, very high common-mode rejection must also be preserved in the differential signal path. While it is very desirable to have a sharp cutoff for the filter, there are no practical circuits that can provide a sharp cutoff with an RC type of filter and still produce 100 dB of common-mode rejection. The compromise solution is to use a two-pole

Fig. 4. Fixed filter SCP.

passive RC filter in front of a unity-gain buffer. Care must be taken in choosing pole positions to provide low enough resistances so as not to introduce further errors caused by bias current offsets in the buffer amplifiers. Overvoltage protection and open transducer detection must also be provided. The total solution is a simple, but functional circuit that is very easily changed for different cutoff frequencies.

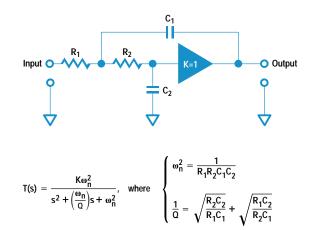

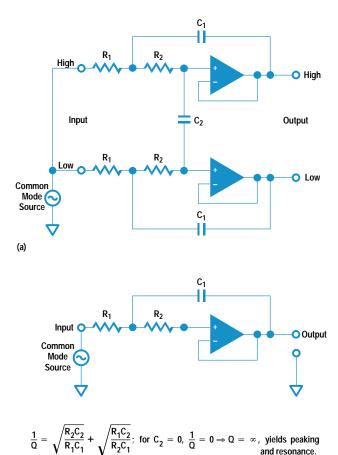

We encountered an interesting phenomenon while developing filter circuits for the fixed filter SCP. A reasonable approach to designing a differential filter is to begin with a single-ended filter (one with the common node at ground) and then transform it into a differential filter. This was the approach originally used to design the fixed filter. The original filter topology chosen was a traditional Sallen and Key structure<sup>1</sup> (see Fig. 5). This filter topology was chosen because of its low parts count and low sensitivities to finite operational amplifier gain-bandwidth and parts variations. The transformation to a differential filter was straightforward and yielded the circuit shown in Fig. 6a. This circuit performed as designed for differential signals but showed anomalies when tested for common-mode rejection.

A spectrum analyzer placed between either output and ground showed a resonance and severe peaking. This anomaly was originally believed to be the result of nonideal behavior in the circuit components. Further investigation showed that this was not the case. There are intrinsic problems with common-mode rejection when using a simple single-ended-to-differential transformation. The equivalent circuit of the

Fig. 5. Sallen and Key filter topology.

**Fig. 6.** (a) The circuit resulting from transforming the filter in Fig. 5 to a differential filter. (b) Equivalent circuit for one half of differential filter.

differential filter with a common-mode signal shows the problem (see Fig. 6b). The behavior of the circuit is such that the voltage drop across  $C_2$  is essentially zero making it appear that  $C_2$  does not exist. In the transfer function  $C_2$  shows up in the damping factor of the complex poles in the half-circuit. As  $C_2$  goes to zero, the damping of the poles goes to zero causing a resonance and the peaking observed. No practical alternative structure was found that did not have a similar difficulty in the transfer function for common-mode signals. As a result of this finding, the circuit in Fig. 4, which has the simpler passive filter with buffer topology, was chosen.

Programmable Gain and Filter SCP. Turbine test customers also want signal conditioning that includes gain as well as filtering to make lower-noise measurements on thermocouples. They want the flexibility to choose different gains and filter cutoff frequencies programmatically. They want this functionality in the same size and channel counts as the straight-through and fixed filter signal conditioning plug-ons. Including this additional functionality and all the other features mentioned above in the same space represented quite a challenge.

The ADC subsystem in the HP E1413 requires gain in powers of two for proper functioning of the engineering unit algorithm, which converts measured voltage data to units such

as ohms or degrees (see article on page 21). Signal gains of 8 and 64 were chosen for the amplification factors. Gains of powers of two allow the engineering unit algorithm to adjust the ADC reading to the actual system gain by simply shifting bits up or down. Since a shift operation is faster to execute than a multiply, the engineering unit algorithm can work at the full speed of the ADC. Gains of 8 and 64 also provide sufficient gain to achieve significant noise reductions without overly complex circuitry.

Since programmability is a requirement, gain and frequencies are switched by analog IC switches. The circuit topology takes advantage of the switch density and configuration (dual 4:1 multiplexer). For the lowest-noise performance and most compact design, all the amplification is done in the first stage of the SCP (see Fig. 7). This allows the use of a single analog switch package to control the channel gain. An additional benefit is that the following low-pass filter section reduces the noise bandwidth of the system after the gain stage, thereby reducing the system noise. This topology is also used in other nonprogrammable gain and filter SCPs.

The filter circuit is the same circuit used in the fixed filter SCP, except that it is programmable. Different resistors are switched into the circuit to change cutoff frequencies. The resistors for the programmable gain and filter circuits are built into custom thin-film resistor packs to conserve space and improve thermal tracking performance. Putting all this circuitry into only 1.5 square inches of printed circuit board space required careful layout and frequent consultation with the production engineer assigned to the project. The resulting SCP stretches the limits of current surface mount technology yet still retains a good measure of producibility.

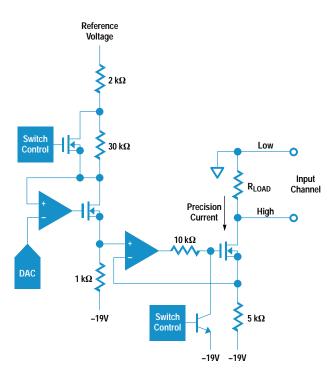

**Current Source SCP.** Turbine test customers need to measure temperatures with thermistors and resistive temperature devices, and resistances of certain types of sensors. To make these resistance measurements, a precision current source with high compliance is required. The design goals for the current source SCP were that the current source would not limit the input voltage range in a four-wire ohms measurement, and that it would provide 16-bit resolution and the ability to measure 100-ohm resistive temperature devices and 10-kohm thermistors. This required the current source to have ±16V compliance, better than 10-ppm resolution, and greater than 1-gigohm output impedance. For the engineering unit algorithm to work at full speed, the current source has to be calibrated and stable during the measurement cycle.

To aid in conversion of the voltage measurement into resistance, current source values of 488.3  $\mu A$  and 30.52  $\mu A$  are used. These sources are programmable to be able to change ranges and turn off the source. Both current sources exhibit low current noise to provide the necessary 16-bit resolution. To put all this capability in a circuit that occupies only 1.5 square inches, we had to design a circuit that used few parts.

Several circuit topologies were tried and discarded for various reasons before the final circuit was designed. The final circuit satisfies all the design goals with a minimum of parts and a simple design (see Fig. 8). It consists of a precision programmable current source driving a high-compliance

(b)

**Fig. 7.** Programmable gain and filter SCP.

Fig. 8. Current source SCP.

current mirror circuit. The precision dc reference is available to the SCP from the ADC circuits. It is used to produce a precise and stable dc current that is adjusted with a digital-to-analog converter (DAC) and controlled by the operational amplifier. Current switching is performed by shunting the 30-kohm resistor to increase the current. The second part of the circuit reflects and scales this precision current and makes it available to the outside world through the MOSFET transistor. Compliance meets the  $\pm 16 \rm V$  goal at extremely high output impedance controlled by the gain of the operational amplifier. Note that this circuit is a current sink rather than a source. This was done to save parts and space.

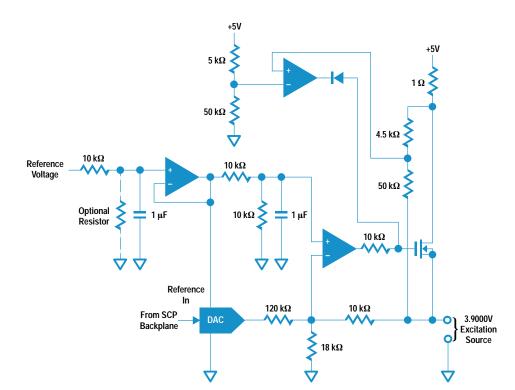

#### Strain Completion with High-Accuracy Excitation Source.

Customers need to measure strain gauges to understand the stresses and loads on turbines. This measurement is typically made with one or more strain gauges configured in a Wheatstone bridge. An excitation supply is needed for the bridge along with completion resistors for making measurements using only one or two strain gauges.<sup>2</sup> To convert bridge voltage readings into strain gauge values, the bridge excitation voltage must be known or measured. To perform engineering unit conversions to strain gauge values at high speed, the excitation source has to be stable and calibrated to a known value to simplify calculations. The excitation supply must be able to source sufficient current to power all

**Fig. 9.** Excitation supply for the strain gauge SCP.

eight strain bridges on an SCP and be able to survive an accidental short circuit without damage. Since only one excitation source was required for each SCP, space constraints were not as critical.

The circuit chosen provides > 400 mA at 3.9000V for excitation (see Fig. 9). The output voltage is calibrated by a DAC to provide this level of resolution. The 3.9000V value was chosen to provide a near full-scale reading on the 4V range. In the event of a short circuit at the output of the excitation source, a fold-back circuit is activated to limit the output current to approximately 75 mA, thus preventing damage to the SCP. Again, the reference voltage provided from the ADC is used as the reference for the excitation supply. It is buffered and then divided down to provide a precise bias voltage for the operational amplifier. A calibration current is sourced at the summing node of the operational amplifier to adjust the output of the excitation source. Note that the calibration DAC uses the same reference as the operational amplifier. This allows the DAC to be used to calibrate any chosen output voltage with the same percentage of calibration span. Pads are provided on the printed circuit board to accommodate different, lower excitation voltages by dividing the reference before buffering. Calibration of the HP E1413 is described in the article on page 25.

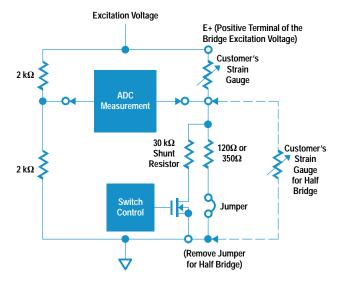

When measuring strain gauges, customers often want to verify that the gauges are properly connected by putting a large-value resistor in parallel (shunt) with one resistor or strain gauge in the bridge. The bridge will then become unbalanced by a predictable amount. The bridge voltage can be measured and compared against the expected amount of deflection to determine if the bridge is operating properly. A large-value resistor and a programmable switch are provided on each channel to perform this task. The shunt resistor is usable in any bridge configuration (see Fig. 10).

#### Other Options

All of the SCPs are designed to accommodate future modifications to the original circuits. Different filter cutoff frequencies, different gains, different output currents, and different excitation source voltages can be accommodated in most cases by simply loading different parts on the printed circuit boards. Pads for other standard-size components are placed on the blank printed circuit boards at strategic nodes to provide for different customer needs with a minimum of additional design time or expense. This has proven to be a popular feature for customers since they can get a custom solution with a minimum of expense and effort.

Fig. 10. Shunt resistor for strain gauges.

#### Conclusion

While the original design goals for the SCPs seemed to be well within reach, the implementation of high-performance circuits capable of providing the needed functionality in the space and at the circuit densities required presented quite a design challenge. High performance was extracted from simple, efficient designs by careful parts choices and placement on the printed circuit boards. Costs were kept low, consistent with the performance required by customers. The results met the original design goals in a way that provides the customer with lasting value.

#### Acknowledgments

I would like to acknowledge the help of my design colleagues on this project as well as our production engineer,

Wes Melander of the Loveland Maufacturing Center, our materials engineer, Beth Delaney, our test engineers, Bert Kolts and Rod Village, and the people in product design services who helped with and designed the printed circuit boards.

#### Reference

- 1. R.P. Sallen and E.L. Key, "A Practical Method of Designing RC Active Filters," IRE Transactions on Circuit Theory, Vol. CT-2, March 1955, pp. 74-85.

- 2. HP Application Note 290-1, *Practical Strain Measurements*, Hewlett-Packard, Part Number 5952-8880, 1981.

# High-Throughput Amplifier and Analog-to-Digital Converter

High system throughput in converting analog signals to digital format in the HP E1413 is achieved by not relying on downstream digital processing hardware and software to compensate for analog anomalies and instabilities.

#### by Ronald J. Riedel

The amplifier and analog-to-digital converter (ADC) section of the HP E1413 provide the interface between the multiplexed analog signals from the signal conditioning pods and the digital world. Some of the functionality provided by this section includes:

- Accepting input signals ranging from a few microvolts to +16 volts

- Correcting for gain and offset errors on a channel-by-channel basis

- Acquiring each multiplexed signal in turn and settling to full accuracy with no memory of the previous channel, even if the previous channel was severely overloaded

- Converting the analog input to a 16-bit digital number with commensurate linearity and accuracy

- Providing a voltage reference, current source, and calibration voltage source for use by the ADC and the rest of the card.

A key contribution to the overall system throughput and customer ease of use of the HP E1413 is that the above functions are provided smoothly and accurately without the need for further error correction by the downstream digital hardware and software. We resisted the temptation to rely on digital processing to compensate for analog anomalies and instabilities, even though this approach would have saved money and time on the analog design.

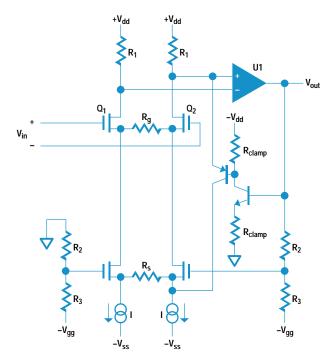

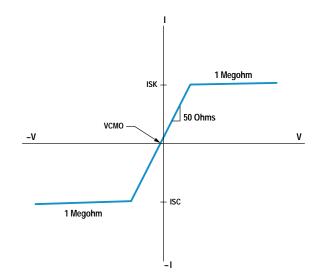

Fig. 1 shows the block diagram of the amplifier and ADC section of the HP E1413.

#### **Amplifier Design and Performance**

The performance requirements of a high-resolution, high-speed scanning voltmeter such as the HP E1413 dictate some fairly challenging criteria for the main input amplifier of the ADC section. In fact, more than any other single piece of analog circuitry, the amplifier can define and limit the performance of the entire system. Some of the design requirements for this amplifier included:

- Fast settling time. To achieve full accuracy on a low-level channel following a high-level channel while scanning at 100 kHz, the amplifier must settle to 10  $\mu$ V after an input of 16 volts, in 10  $\mu$ s. This represents settling to better than 1 ppm in less than 10  $\mu$ s.

- Fast overload recovery. So that an overloaded channel does not affect measurements on subsequent channels in the scan list, the amplifier must recover from overload quickly and

Fig. 1. HP E1413 analog-to-digital converter block diagram.

cleanly. Our goals were recovery to linear operation in less than 1  $\mu s$  and full settling in less than 10  $\mu s$ .

- Fully balanced differential inputs. The HP E1413 resolves signals down to 2  $\mu$ V with a "straight-through" signal conditioning plug-on. However, because of the high conversion rate we cannot use the normal noise reduction techniques of integration, filtering, and averaging. Fully balanced differential inputs are necessary to achieve adequate noise rejection and to eliminate ground loops from the measurement path. The straight-through SCP is described in the article on page 9.

- High common-mode rejection ratio. A high common-mode rejection ratio is necessary for good noise rejection and to allow measurement of sensors such as strain gauges, which typically involve a small differential signal (in the order of

millivolts) impressed onto a large (several volts) dc commonmode signal. Our design goal for common-mode rejection ratio was greater than 120 dB up to 60 Hz on the most sensitive (62.5 mV) voltage range.

- Low noise. Once again, standard noise reduction techniques of averaging, filtering, and integration are not normally available in high-speed scanning applications. Thus, a low-noise amplifier is essential if the full resolution of the HP E1413 is to be usefully realized. Our design goal was a noise level of less than 5  $\mu$ V rms referred to the input of the amplifier.

- Autoranging with no loss of scanning speed or accuracy. In a scanning system, a customer may connect channel 1 to a thermocouple generating 1 mV and use channel 2 to monitor a 10-volt power supply. The amplifier must be able to range between these two signals at speed, without degrading system accuracy. Also, many customers may be unsure as to the exact voltage expected on a given channel. Autoranging allows them to let the HP E1413 select the optimum measurement range on a sample-by-sample basis. The customer's measurement task is greatly simplified if there is no need to give up speed or accuracy to use autoranging.

- Linearity and accuracy commensurate with a 16-bit system.

Our goal was to provide 0.01% overall system accuracy.

- Good dc performance. For all of its high speed, the HP E1413 still has the requirement to be a good dc voltmeter. Thus, low drift (<10  $\mu$ V/°C) and low bias currents (<1 nA) are essential.

- 16-volt differential and common-mode input range. For many applications, particularly in the automotive world, the standard input limits of ±5 volts or ±10 volts seen on many high-speed ADC systems simply are not adequate. We set a goal to provide a full ±16-volt input range so that 12-volt and 14-volt buses can be measured without the use of cumbersome speed and accuracy limiting attenuators.

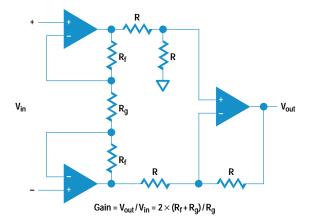

While none of the performance requirements mentioned above are particularly difficult to achieve in isolation, satisfying all of them simultaneously proved much more challenging. Initially, it seemed to make sense to attempt to implement the amplifier using the classic three-operational-amplifier circuit shown in Fig. 2 with off-the-shelf parts. However, an exhaustive search of manufacturers' catalogs soon revealed that commercially available opamps couldn't do the job. All the parts we considered suffered from one or more of the

Fig. 2. Classic three-opamp instrumentation amplifier.

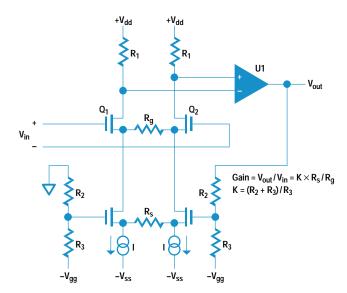

Fig. 3. Basic current-mode instrumentation amplifier.

following limitations: poor settling time or overload recovery, excessive input bias currents, inadequate common-mode rejection ratio, or limited input voltage range.

Another avenue, which involved using a monolithic instrumentation amplifier, was also considered. However, these parts typically require a switch with low resistance and low capacitance such as a relay to switch the gain accurately. This made them useless for meeting our autoranging requirements.

For these reasons, we determined that a discrete amplifier design would be necessary. The amplifier uses a classic current-mode instrumentation configuration, with a special gain switching circuit that is both fast and accurate. It implements overload clamping in such a way as to greatly reduce recovery time by eliminating internal saturation and nonlinear operation. Finally, the amplifier provides for "on-the-fly" gain and offset correction on a per-channel basis so that the ADC sees an accurate signal for conversion. This eliminates downstream time-consuming digital processing to correct the readings for gain and offset errors and allows the full range of the ADC to be used for measurements.

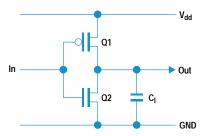

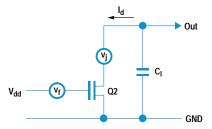

Fig. 3 shows a simplified schematic of the basic current-mode instrumentation amplifier. Because of the feedback action of opamp U1, matched input FETs  $Q_1$  and  $Q_2$  operate at constant, equal currents. Thus, the voltage impressed across  $R_g$  is equal to the input voltage with a common-mode shift equal to the  $V_{gs}$  of the input FETs. The current through  $R_g$  becomes  $V_{in}/R_g$ . This current must flow back through  $R_s$  to keep the lower current sources satisfied. The output of U1 will servo to make this happen, resulting in an input/output transfer function of:

$$V_{out}/V_{in} = K \times R_s/R_g$$

where

$$K = \frac{R_2 + R_3}{R_3}$$

Thus, the amplifier gain is controlled entirely by the value of K and the ratio of  $R_{\text{S}}$  to  $R_{\text{g}}$ . K and  $R_{\text{S}}$  influence the bandwidth

#### **Binary Ranges Speed Processing**

Referring to Fig. 3 in the accompanying article, for the HP E1413  $R_{\rm S}$  is fixed at 600 ohms.  $R_{\rm g}$  has values of 55.555 ohms, 222.22 ohms, 888.8 ohms, 3.555 kilohms, and 14.222 kilohms, and K = 6.6667. This gives amplifier gains of 72, 18, 4.5, 1.125, and 0.28125. Since full-scale at the ADC is 4.5 volts, this gives full-scale input voltage ranges of 62.5 mV, 250 mV, 1 volt, 4 volts, and 16 volts. At first glance, these full-scale ranges may seem odd; why not choose a more common 1,3,10 or 1,2,5,10 sequence? These values were not chosen for ease of human comprehension, but to interface well to a binary number system. The ranges have full-scale values of  $2^{\rm n}$ , where n has values of -4, -2, 0, 2, and 4, so the digital reading from the ADC maps directly into the mantissa of an IEEE floating-point number with no further processing required beyond right or left shifts for normalization. This greatly relieves the burden on the downstream processing hardware, freeing it for more productive tasks.

and stability of the amplifier and are normally not varied for a particular design.  $R_g$  is used to set the gain because, to a first approximation, bandwidth, settling time, and stability are independent of  $R_g$ .

Also notice that ideally the amplifier has no gain for common-mode signals, resulting in a theoretically infinite common-mode rejection ratio. Obviously, there are realworld limitations, which will be discussed later.

Several additions had to be made to this basic amplifier architecture to allow it to meet the performance demands of the HP E1413. The first is a viable means of accurate, high-speed range switching. Simply using several series FET switches to switch in various values of  $R_{\rm g}$  is not workable. The lowest value of  $R_{\rm g}$  used in the HP E1413 is 55 ohms. Any series FET used to switch this resistor in and out of the circuit would have to have an on resistance of much less than one ohm to meet gain accuracy and stability requirements. Such a FET would inherently have a large parasitic capacitance of many hundreds of picofarads, which would destroy amplifier stability, bandwidth, and settling time if used in that area of the circuit.

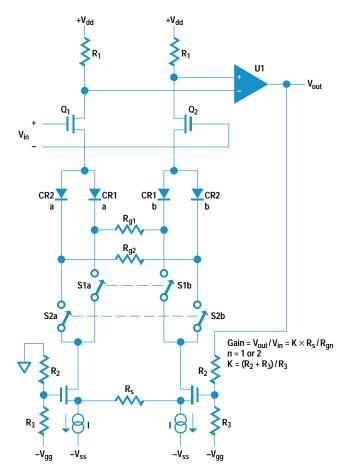

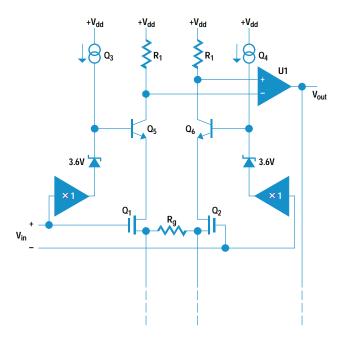

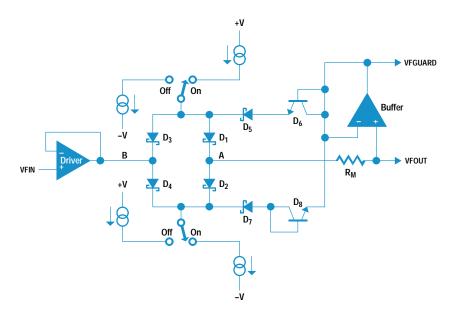

To meet the performance requirements of the HP E1413, an arrangement of current-steering diodes and small geometry FET switches are used to switch the amplifier gain. Fig. 4 shows a simplified form of this circuit involving two gain ranges. Switches S1a, S1b, S2a, and S2b are small-geometry FETs with channel capacitances around 5 pF and on resistance of 50 to 100 ohms. Since these FETs are in series with the very high impedance of the lower current sources, this range of on resistance has a negligible effect on circuit performance.

As an example of the operation of the circuit shown in Fig. 4 assume that S1a and S1b are on, and S2a and S2b are off. There is then a current path through CR1a and CR1b, enabling  $R_{g1}$  to control the gain.  $R_{g2}$  is effectively isolated by the back-to-back diodes CR2a and CR2b and the off switches S2a and S2b. CR1a and CR1b operate at constant current, as do  $Q_1$  and  $Q_2$ , so that diode nonlinearities have no effect. It is important that the diodes track with temperature since the amplifier input offset voltage is a direct function of the difference between the forward voltage drops of the on diodes.

This gain switching arrangement provides the high switching speed, good settling, and gain stability required for the HP

**Fig. 4.** Basic (2-range) range switching scheme for the current-mode instrumentation amplifier.

E1413. It also allows us to meet our goal of autoranging at the full 100-kHz scanning speed without compromising accuracy.

For an amplifier to recover rapidly and gracefully from an input overload, it is important that the internal biasing be upset as little as possible when such overloads occur. In the HP E1413, this is accomplished by a special set of clamp circuits that do more than simply limit the input or output voltages. During an overload condition, bias current is simply routed around the gain section instead of through it. This has the effect of reducing the gain to whatever value is necessary to keep the output in the linear region. At the same time, the lower current sources and the output opamp see no change in operating conditions compared to a normal input. Thus, these critical parts of the amplifier are not upset during an overload and recovery is rapid and uneventful (see Fig. 5).

Buffering of the input FETs from common-mode voltage changes is important to achieve the desired high-level common-mode rejection ratio. In the circuit shown in Fig. 3 these FETs will see the entire common-mode voltage as a change in their  $V_{\rm ds}$ . Unless the FETs are perfectly matched (an impossibility), this will result in a change of input offset voltage, which will in turn translate into a small differential input signal as the result of the changing common-mode signal.

To prevent this, a cascode arrangement is used (see Fig. 6). The combination of current sources  $Q_3$  and  $Q_4$ , along with

Fig. 5. Amplifier overload clamping technique (only positive clamp is shown).

bipolar pair  $Q_5$  and  $Q_6$ , provide a stable, fixed  $V_{ds}$  for input FETs  $Q_1$  and  $Q_2$  regardless of the common-mode voltage. Thus, since  $Q_1$  and  $Q_2$  are isolated from common-mode inputs, their offset does not change, and the common-mode rejection ratio remains very high.

The result of all of this careful and sometimes subtle design work is an amplifier that occupies about 2.5 in<sup>2</sup> of printed circuit board area, draws about 300 mW of power, and

Fig. 6. Upper FET bias scheme for high common-mode rejection ratio.

meets or nearly meets all of the performance criteria outlined above. It is this sort of meticulous design that makes the HP E1413 not just another plug-in ADC card, but a dependable, accurate, information gathering system free from pitfalls and hidden problems for the user.

#### Calibration, Pipelining, and Timing

On-the-fly gain and offset correction, which is done in hardware in the analog domain, is an important feature of the HP E1413. It may seem old-fashioned to use analog hardware for this purpose in today's world of high-speed number-crunching, but there are some advantages. First, it relieves the downstream digital processing hardware of this task, freeing system resources for more complex tasks such as sensor linearization, engineering unit conversions, and so on.

Secondly, it is useful to recognize that the most fundamental limit on system resolution and dynamic range is the 16-bit analog-to-digital conversion process. Any uncorrected gain and offset errors that occur before the ADC subtract directly from this dynamic range. For example, assume we were doing digital gain correction after the ADC and the uncorrected gain was high by 5%. If a customer tried to measure a 15.9-volt signal in this case the result would be an overrange because 15.9 volts times 1.05 = 16.69 volts, which is above the ADC input range of 16 volts. In fact, for this example, the maximum input voltage that can be measured is only 15.24 volts. This is confusing and frustrating for a customer who presumably ordered and expected to get a 16-volt ADC. Even more confusing, a second unit, presumably identical, might have an uncorrected gain error of 5% low. This unit would then measure up to 16.84 volts before showing an overload.

This kind of customer confusion and uncertainty is unacceptable for high-quality instrumentation. The customer should not have to think about such issues. Analog correction ahead of the ADC process eliminates these issues.

Thirdly, analog offset correction allows us to remove large fixed sensor offsets at the amplifier front end, using the TARE:CAL function. This function allows the customer who is only interested in monitoring changes in sensor output rather than absolute value to increase measurement resolution. This is particularly useful with sensors such as strain gauges. Tare calibration is described in more detail in the article on page 25.

Fig. 1 shows the blocks belonging to the gain and offset calibration subsystem. A local RAM stores a separate 12-bit gain correction constant for each of the five amplifier ranges and each of the 64 channels ( $64 \times 5 = 320$  gain calibration constants in all). The RAM also stores two offset correction constants for each range and channel (an 8-bit coarse constant and a 12-bit fine constant). This allows us to correct gain errors of up to  $\pm 5\%$  and offset errors of up to  $\pm 25\%$  of full scale. This relatively large amount of correction range makes the calibration system very robust and able to accommodate a wide variety of signal conditioning plug-ons and sensors. All of these calibration constants are derived automatically during the various system autocalibration functions based on a few fundamental calibration factors measured during factory or calibration laboratory calibration.

Fig. 7. Timing diagram of an HP 1413 measurement cycle.

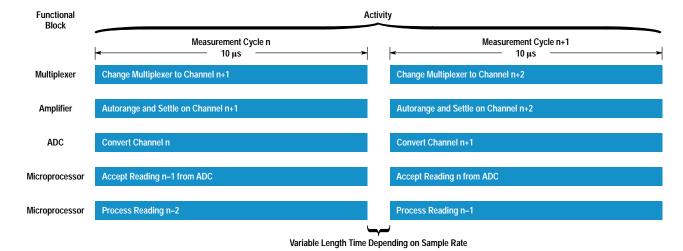

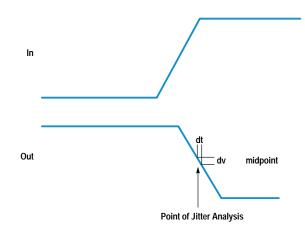

Gain and offset correction are interwoven into the measurement cycle such that no speed penalty is incurred. Fig. 7 shows a simplified timing diagram of a typical HP E1413 measurement cycle. An overlapped, or pipelined approach is used so that several operations happen at once.

For example, assume a channel list of eight channels numbered 1 through 8. If at some point during the scan we were to take a snapshot of activity in the HP E1413, we might see the following operations happening simultaneously during a single  $10~\mu s$  period.

- The multiplexer has switched to channel 6, and the amplifier is autoranging, settling, and applying gain and offset corrections to that channel.

- The sample and hold circuit in the ADC has acquired channel

5, and the ADC is converting this channel to a 16-bit digital

word, which will be temporarily stored in the ADC.

- The digital value of channel 4, which has been stored in the ADC since the last measurement cycle, is being transferred to the onboard microprocessor for further processing.

- The onboard microprocessor is processing the reading from channel 3 and transmitting it to the onboard FIFO and current value table\* for access by the host computer.

During the next 10- $\mu$ s measurement cycle, the multiplexer will switch to channel 7 and all other activity will move up one step in the pipeline. This pipelining approach allows the HP E1413 to maintain system throughput at 100,000 readings per second, even though the required operations for a single reading take much longer than 10  $\mu$ s.

Fortunately, the customer sees none of this complexity. The task of keeping track of all readings and indexing them properly to each channel is taken care of by the onboard microprocessor. This microprocessor also ensures that the pipeline is properly flushed at the beginning and the end of a scan so that no stale readings are transmitted at the beginning of a scan and no good readings are left stranded at a scan's end.

On the HP E1413, a Xilinx FPGA (field-programmable grid array) handles all sequencing and timing of the ADC and amplifier section, including:

- Multiplexer update and channel advance

- · Autorange detection and timing

- Calibration RAM interface

- Digital-to-analog converter updates for gain and offset correction

- Start pulse to the ADC.

Using an FPGA for this purpose gave us great flexibility in the design process and reduced the number of required printed circuit board patches and turn-arounds during the prototype phase of the project.

#### Acknowledgments

Several people deserve thanks for their key roles in this project. They include Don Miller, former section manager, out of whose vision came the whole HP HD2000 effort, Von Campbell, project manager, for his capable management of this project and for keeping us all on track and on schedule, Bert Kolts, test engineer, Vic Anderson, support technician par excellence, and Barb Haas and Anita Helme, who made sure all the parts arrived to build the prototypes on schedule.

<sup>\*</sup> A current value table is an area of RAM that is accessible to the onboard microprocessor and the host computer. This table stores the most recent reading (current value) for each channel. For monitoring purposes a customer can directly access the most recent readings on any channel without having to sort through possibly hundreds or thousands of readings in the FIFO buffer.

# On-the-Fly Engineering Units Conversion

An algorithm has been developed that provides engineering units conversion in real time (10 microseconds) in the HP E1413 scanning analog-to-digital converter instrument. The algorithm converts numbers to IEEE 754 standard 32-bit floating-point format.

#### by Christopher P.J. Kelly

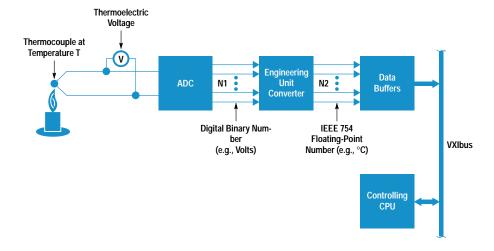

The HP E1413 is a VXIbus 64-channel scanning analog-to-digital converter (ADC) that is used in data acquisition applications. These applications usually measure real-world phenomena such as temperature using a variety of transducers. These transducers (e.g., thermocouples) convert the phenomenon of interest into a voltage, which is connected to a channel of the ADC. The ADC then converts this voltage into a binary digital number that represents the voltage applied to its input. In Fig. 1, for example, the temperature T of a flame is sensed by a thermocouple. The thermoelectric voltage V is applied to the ADC, which generates a digital binary number N1 whose value is determined by V, so its units are typically microvolts. The challenge is to provide a fast engineering units converter to change N1 into a floating-point number N2 in units of temperature such as degrees Celsius.

In the thermocouple example, the relationship between temperature and thermoelectric voltage is described by NIST (the U.S. National Institute of Standards and Technology, formerly National Bureau of Standards) using a high-order polynomial. For a type E thermocouple, for example, NIST models its thermoelectric behavior using a 13th-order polynomial. Considerable computing power is required if this polynomial must be evaluated in real time (10 microseconds in the case of the HP E1413).

#### **Need for Conversion**

Why is engineering units conversion important? The reason lies in the nature of the task of continuous on-line data acquisition and the coupling between the instruments and the controller in a VXIbus instrument system.

In continuous on-line data acquisition, measurements are made and recorded continuously for an indeterminate period of time. During this period, data may also be displayed for operators or used for adjustment of the experimental conditions (control). The data should be available in useful and understandable units of measure so that operators and control systems can view and operate upon it easily. Recorded data also should be in a form such that no additional processing is required for the data to be useful, thus helping ensure the correctness of experimental results. For short-duration experiments the data may be buffered in a raw format while a converter slowly massages it into a useful form. But when data is acquired continuously, the acquisition system must be able to convert the data at full speed or eventually the buffers will overflow.

The VXIbus architecture also allows a new, tight coupling between instruments and their controlling CPU. This permits a large increase in system throughput if the instruments are

**Fig. 1.** The components involved in converting a temperature measurement into a floating-point number.

designed to take advantage of the architecture. In some non-VXIbus instrument systems the instruments are coupled to the controller using a communications link, and control or data messages are exchanged by explicit input/output transactions. However, in a VXIbus system the controller can be connected to the VXIbus backplane through its address and data bus, and the instruments' control and data registers appear as memory addresses in the memory map of the VXIbus CPU. In many cases, the CPU actually plugs into the VXIbus cardcage and draws its power from the backplane. In this model, no explicit I/O transactions are required to operate the instruments, so no I/O device drivers or layers of communications protocol are needed, and operations can proceed at full computer backplane speeds.

With this tight coupling between the computer and its instruments, if the instrument is designed to behave like a memory device, the control program can access real-time data at full CPU speeds as if the instrument were part of its memory. If the data is in a computer-native format, the computer can store, display, and manipulate the data immediately, with no format or units conversion. For most of today's computers the IEEE 754 standard floating-point number format is native and is operated upon directly by the floating-point processor in the CPU. If the instrument is able to transfer its measurements in this format, the computer has no burden of translation from a special format to one it can process directly. This means that data can be acquired more rapidly and tighter experimental control can be maintained than with alternative systems of similar cost.

In previous systems, these tasks were often handled by the controlling CPU if the data was required in real time. As data rates rose, considerable CPU power was necessary to do all these tasks in the available time. Some systems used multiple CPUs to handle the load, but the overhead of synchronization and communications among the CPUs also grew to absorb a considerable fraction of the available processing power.

The goal of the HP E1413 engineering units converter is to make it possible to realize the full speed potential of the VXIbus architecture by providing all necessary conversions in the instrument in real time. Each of the 64 input channels requires its own engineering units conversion since transducer types or calibration may vary from one channel to the next. For the HP E1413 this means 100,000 measurements per second are converted to engineering units, formatted according to IEEE 754, and made available to the controller over the VXIbus backplane. 100,000 measurements per second means 10 microseconds per measurement.

#### **Bounding the Problem**

Upon first examination of the challenge of on-the-fly engineering units conversion for this product, several factors worked to simplify the problem. First, the ADC only produces a 16-bit binary number as a result of the conversion, meaning that the technique used for the engineering units conversion does not need to exceed 16 bits of resolution. Whatever format is used for reporting results, the measurement itself is intrinsically resolved to one part in  $2^{16}$  (65,536). The second mitigating factor is that although the ADC has five operating voltage ranges, these ranges are related by powers of two. This means that changing ranges only requires

shifting the 16 bits from the ADC right or left in an accumulator to maintain correct measurement scaling. Finally, the entire scanning ADC system is calibrated in true volts. This calibration includes multiplexers, filters, attenuators, and gain stages all the way back to the transducer wiring. Every channel is individually calibrated to measure voltage applied to its input terminals. This corrects for any channel-to-channel variation in offset voltages resulting from relay contact thermoelectric voltages and variations in the amplification of the signal-conditioning channel amplifiers. Thus, no postmeasurement correction is necessary, allowing the measurement to proceed at maximum speed.

This third factor means that all engineering units conversion coefficients can be calculated in advance, referenced to absolute voltage. If the system were calibrated in some arbitrary ADC voltage units, we would require dynamic computation of coefficients based on the state of calibration of each individual ADC, a production engineering nightmare.

Efforts have previously been made to speed up engineering units conversion in similar systems, and a variety of shortcut techniques have been developed. These techniques generally trade off accuracy, speed, and memory table size, and each technique has strengths and weaknesses. These techniques include development of low-order polynomials to approximate the NIST equations with fewer terms and hybrid lookup-table-with-correction-factor techniques. In the limit, it is possible to perform simple table lookup, with the ADC reading being used as an address index into an array of results. This technique is very fast, but uses a lot of memory for the lookup tables. In the case of the E1413, with 16 bits of resolution and 64 separate channels, this technique would have required 16 megabytes (64 channels × 16 bits of resolution  $\times$  4 bytes per result =  $64 \times 65536 \times 4 = 16$  megabytes) of tables, too expensive a solution. On the whole, we needed a technique that would precompute as much of the problem as possible, leaving little remaining work to be done in real time.

#### **New Algorithm**

The HP E1413 engineering units conversion algorithm uses a linear approximation technique to convert the ADC binary voltage numbers into engineering units. The technique divides the operating voltage range of the ADC into a number of segments of equal size and fits a straight line to the data in each segment. The number of segments can be adjusted to provide an acceptable level of conversion error, with more segments yielding lower error. In our case, we found that 128 segments were sufficient to limit errors to acceptable limits.

In Fig. 2, the algorithm is represented schematically. On the left, a digital binary number from the ADC is divided into two sections. The high-order bits are used to address a table of engineering units conversion coefficients. The low-order bits enter the numeric processing pipeline and are multiplied by the slope coefficient for this table segment, resulting in the product (P). This product is then added to the offset coefficient for this table segment, which represents the value of the engineering units conversion equation at the beginning of the segment. The result  $(R_0)$  is now in engineering units, and in a simple model can be used as output. This process of lookup, multiply, and add can be accomplished

Fig. 2. A block diagram of the engineering unit conversion process.

very quickly compared to evaluation of a high-order polynomial. In fact, the process is simple enough to be performed entirely in a simple hardware state machine consisting of ROM, multiplier, adder, and clock control devices.

In the HP E1413, additional steps are added to keep the resolution of the conversion up to an acceptable level. In general, an engineering units conversion equation will have relatively high slope coefficients in some parts of the curve and relatively low slope coefficients in others. The comparative sizes of the slope and the offset will also change over the width of the conversion curve. To keep the resolution of the conversion process up to acceptable levels when using integer arithmetic, the HP E1413 conversion also includes a third, scaling, coefficient. This factor is used to adjust the scale of the slope and offset coefficients, and is corrected for in a postconversion rescaling (right or left shift as appropriate). The scaled result ( $R_1$ ) is then reformatted according to IEEE 754 before the result ( $R_2$ ) is presented to the controlling CPU.

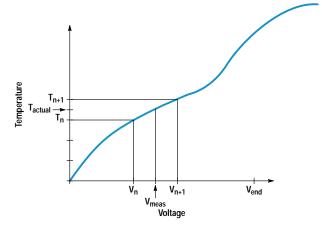

To show graphically how the algorithm operates, Fig. 3 shows the thermoelectric voltage curve for a hypothetical temperature transducer. On the vertical axis we see temperature and on the horizontal axis we see the resulting voltage. The curve illustrates a nonlinear relationship between temperature and voltage. When the ADC measures the transducer, it puts out a digital binary number  $V_{meas}$ . When this voltage is presented to the engineering units converter, it is found to fall into voltage segment n, because its voltage lies between the beginning voltage of the segment  $(V_{n+1})$ . When the engineering units

Fig. 3. Thermoelectric voltage curve for a hypothetical temperature transducer.

converter receives  $V_{meas}$ , it divides it into high-order bits, which have a value of n, and low-order bits, which indicate how far into the  $V_n$  segment the actual voltage lies.

The engineering units converter next uses the high-order bits to look up the nth segment slope coefficient from the conversion table. The slope coefficient is multiplied by the low-order bits, whose value is  $(V_{meas} - V_n)$ . The product of this multiply has a value of  $(T_{actual} - T_n)$  on the vertical axis. That is to say, the product is equal to the distance above the base temperature of the segment where the true temperature lies. The second step of engineering units conversion is to fetch the offset coefficient  $(T_n)$  from the coefficients lookup table and add it to the product of the multiply. The result of this addition is now in units of temperature. This value is now scaled and converted to floating-point number format, and is available for use by the controlling CPU.

#### Results

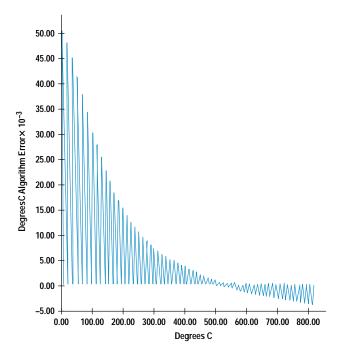

The multiply-add sequence is a core function in most digital signal processing (DSP) algorithms. It is a function optimized by most DSP processor chips into a very fast operation. This makes the architecture of DSP processors well-suited to the engineering units conversion algorithm, for which multiplication, addition, and speed are all important. The HP E1413 uses a Texas Instruments TMS320C51 DSP processor chip as its onboard CPU, and is able to execute this algorithm in the available 10 microseconds, along with other functions such as measurement sequence control. The processor also handles measurement trigger counting and timing functions during measurement sequences and calibration and measurement setup commands when the instrument is not actively acquiring data.

As mentioned above, the algorithm can be adjusted to trade conversion accuracy for coefficient table size. In the HP E1413, the algorithm divides the engineering units space into 128 segments, which yields 512-word conversion tables for each transducer. Since the thermocouple is one of the target transducers for this product, it is instructive to evaluate the errors generated by the algorithm when using thermocouples. Fig. 4 shows a graph of the algorithm errors when the transducer is a Type E thermocouple. The largest errors occur near 0°C and are nearly 0.05°C. Over most of the temperature range the errors are below 0.005°C, far below the ASTM

Fig. 4. Engineering unit accuracy with a Type E thermocouple.

manufacturing error specification for the thermocouple wire itself, which rises to  $\pm 4.4^{\circ}\text{C}$  above 800°C.

The shape of the error curve is determined by the rate of change of the thermoelectric voltage for the thermocouple over temperature. The thermoelectric voltage change per degree of temperature change is called the Seebeck coefficient of the thermocouple. As the Seebeck coefficient changes, the algorithm must approximate a curving line segment with a straight line. This leads to a small error in the middle of the line segment, with almost zero error at the endpoints. The greater the curvature of the function being approximated, the greater the error. The errors generated by the conversion algorithm are far below the measurement errors of the analog hardware or those of the transducers themselves.

#### **Summary**

The new segmented linear approximation algorithm allows real-time conversion of analog measurements into engineering units. The algorithm provides ample conversion accuracy for the target hardware and transducers, and executes in less than ten microseconds using the microprocessor in the instrument. Performing this conversion in the instrument allows the complete measurement system to make usable measurements faster and at lower system cost than was possible with previous instruments.

#### Acknowledgments

Thanks to the whole HP E1413 design team for their cooperative can-do attitude throughout this project. This project has been a challenging and enjoyable experience, and I have been privileged to work with such fine people.

# Built-In Self-Test and Calibration for a Scanning Analog-to-Digital Converter

Onboard calibration capability enables the HP E1413 to calibrate all 64 input channels in under 15 minutes, many times faster than the manual calibration techniques previously required in similar systems.

#### by Gerald I. Raak and Christopher P.J. Kelly

The HP E1413 is a 64-channel scanning analog-to-digital converter (ADC) with configurable signal conditioning plug-on (SCP) circuits. The HP E1413 combines signal conditioning, analog multiplexing, analog-to-digital conversion, and digital data processing in one integrated subsystem. Similar subsystems are made up of separate components, often combined by the end user. In such systems it is difficult for the designer of one component to provide end-to-end calibration and self-test since the designer has no control over the design of some components. Final integration is often left to a system integrator or to the end user, who must then add hardware and software engineering to make the system fully functional. Calibration of high-channel-count data acquisition systems of this sort may take many hours or even days, which drives up the cost of ownership.

With design control of all four major components, the HP E1413 design team was able to add considerable value by integrating these components and their interaction during calibration, self-test, and measurement operations. This is accomplished using additional calibration hardware and software that enable stimulus and measurement access to all major components of the measurement hardware.

#### Calibration and Self-Test Hardware

Three major hardware components were added to the HP E1413 to enable self calibration and test: onboard voltage and resistance reference sources, a calibration bus that connects sources to various points in the circuit, and multiplexers and relays to control measurement and source signal routing.

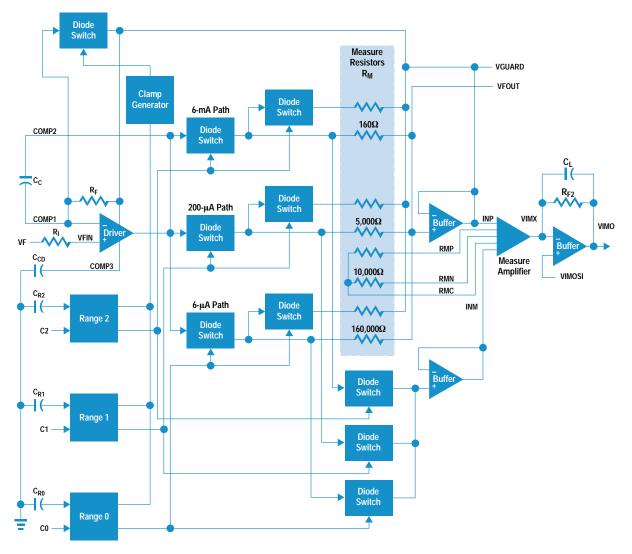

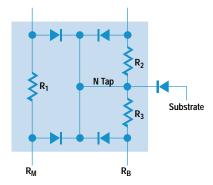

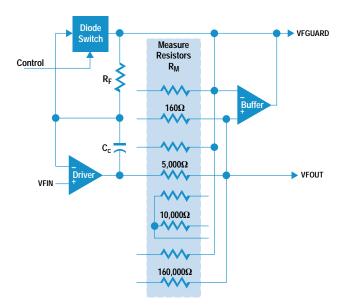

Fig. 1 shows a simplified diagram of the HP E1413 calibration hardware. The voltage and resistance source section provides a precision 7500-ohm resistor, a programmable voltage source, and a short circuit (zero voltage) reference. The calibration bus (CALBUS) connects the various sources either to the input of the signal conditioning plug-on boards or to an external multimeter via the front-panel connector. The 64 calibration relays serve two purposes: first, to allow calibration sources to enter the signal conditioning of a channel, and second, to isolate the HP E1413 input stages from the customer wiring when power is lost or when excessive input voltages are detected. The semiconductor multiplexers MUX B and MUX C allow the reference sources to be connected to the calibration bus or directly into the ADC input amplifier stage.

#### **Different Types of Calibration**

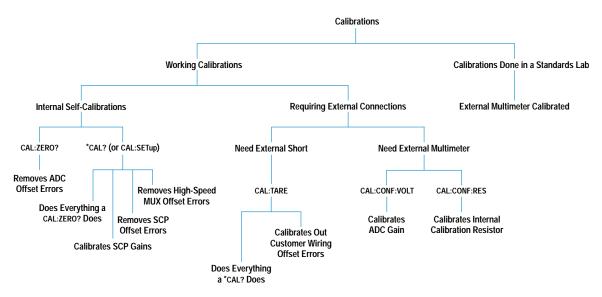

The objectives of the HP 1413's built-in calibration are to provide high measurement accuracy and to make calibration simple and fast for customers, including measurement systems with more than one HP E1413. The calibration tree in Fig. 2 shows that there are several types of calibration available for the HP E1413. The three main types are calibrations using an external standard multimeter, working calibrations including those done using the multimeter, and internal self-calibrations. Fig. 3 shows the HP E1413 components calibrated by these different calibration types.

Working calibrations and internal calibrations are depicted in Fig. 3 as nested boxes because these calibrations are related in a hierarchical manner. Subsets of these major calibrations are accessible to the customer because their speed and convenience make them individually useful (see "A Hierarchy of Calibration Commands," on page 28). For best results, internal self-calibrations and working calibrations should be performed in the HP E1413 working environment. This means the HP E1413 should be warmed to normal operating temperature with normal operating airflow from the VXIbus cardcage. There can be significant temperature and airflow differences inside a VXIbus mainframe between a standards laboratory environment and the working environment depending on ambient temperatures and how many cards are loaded into the VXIbus mainframe. An external multimeter with its heated reference and internally controlled airflow can handle these environment changes better than an HP E1413.

As the first stage of calibration, the external transfer standard digital multimeter should be calibrated in a standards laboratory. This multimeter should be a 6½-digit (21-bit) or better multimeter (such as the HP E1410 or the HP 3458A digital multimeters). The external multimeter is then taken to the HP E1413 operating environment where it can be used to calibrate multiple 16-bit HP E1413s. This makes the standards laboratory's calibration easier, and an HP E1413 calibrated in its working environment will be more accurate in that environment. In some systems, the digital multimeter is dedicated to the test system and wired to the HP E1413 calibration bus connectors and is only removed when the multimeter requires recalibration.

Fig. 1. A block diagram of the HP E1413 circuits used for calibration and test.

Fig. 2. HP E1413 calibration tree.

#### **External HP E1413 Working Calibrations**

External working calibration of the HP 1413 requires a multimeter to establish ADC gain calibration and the exact value of the precision resistor in the HP E1413. The ADC gain calibration forces the gain of the HP E1413 ADC to match the gain of the external multimeter on each of the five measurement ranges of the HP E1413. This calibration takes less than

five minutes using an external controller sending a sequence of setup and measure commands for each measurement range.

In the following discussion it is assumed that the multimeter is an HP 3458A DMM or other HP bench-type multimeter. Other types of multimeters may require different connections.

**Fig. 3.** Areas of the HP E1413 affected by the different calibration types.

#### **A Hierarchy of Calibration Commands**

Calibration of the HP E1413 ADC module can be performed using only one external instrument, a digital multimeter. As implied in Fig. 2 in the accompanying article there is a hierarchy of calibration types in the HP E1413 that can be invoked by the calibration commands.

At the highest level are calibration commands that evaluate the HP E1413 transfer-standard components. These commands, which include CALibrate:CONFigure:VOLTage and CALibrate:CONFigure:RESistance, allow an external digital multimeter to make measurements to establish the value of key parameters in the HP E1413 circuitry. These key parameters are the ADC input amplifier gain on each of five ranges and the value of the precision resistor in the HP E1413. All other HP E1413 calibrations are based on these six parameters.

Below these calibrations are the working calibrations, which include CAL:TARE, \*CAL?, and CAL:ZERO?. These calibrations affect smaller and smaller parts of the HP E1413 and are shown in Fig. 2 as being entirely contained within the previous type of calibration. The innermost (smallest span) calibration is CALibrate:ZERO?. CAL:ZERO? is used only to correct the ADC for drift in voltage offset, which usually results from temperature change. This command is very fast (less than five seconds) and can be executed frequently to compensate for any changes in the temperature or flow rate of the air cooling the HP E1413.

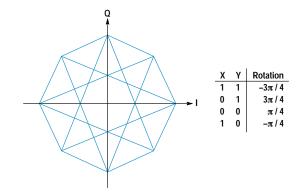

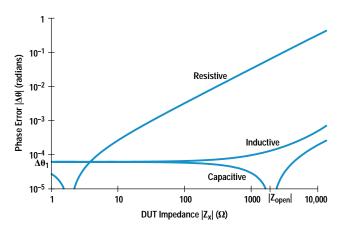

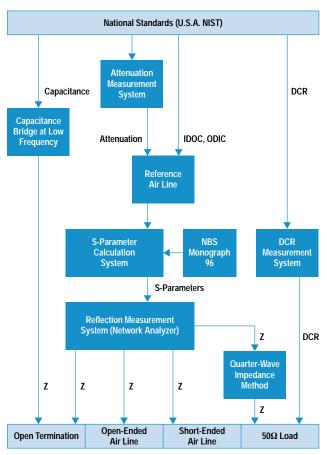

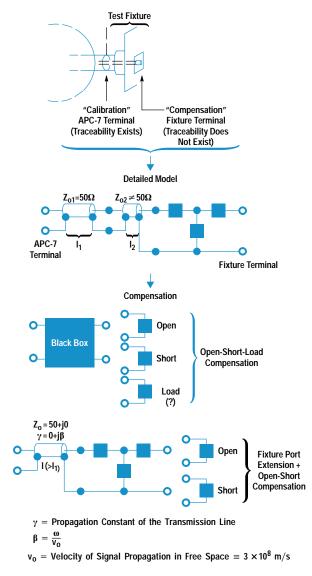

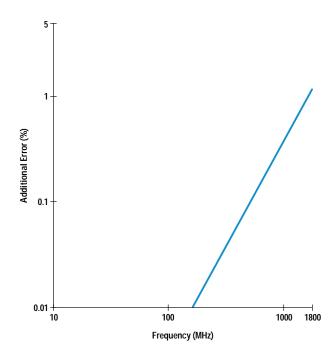

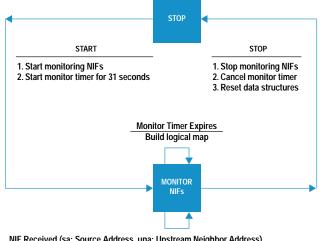

The \*CAL? command is used to correct for any voltage offset caused by the SCPs or the 64-channel multiplexer, and for any gain errors in the SCPs. For example, if channel 1 of a SCP has a nominal gain of eight but an actual gain of 7.998, the \*CAL? command will correct for the difference by adjusting the ADC input amplifier gain upward by a factor of 1.00025 whenever channel 1 is being measured. Every channel containing an input SCP is calibrated this way during the execution of the \*CAL? command. Since up to 64 channels are calibrated, the \*CAL? command can be time-consuming, usually requiring 5 minutes or more to complete. The onboard current source and any current or voltage sources on the SCPs are also calibrated during \*CAL?. Fig. 3 in the accompanying article shows that CAL:ZERO? is also performed by \*CAL?.